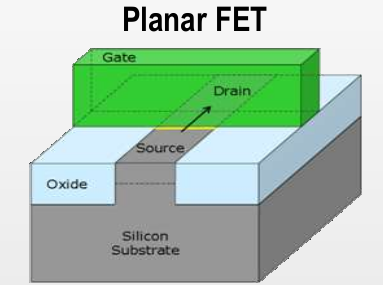

i) Planar Fin FET = single gate

- Single gate channel control is limited at 20nm and below

- Increasing sub-threshold leakage

- Increasing gate leakage

- Decreasing mobility

ii) Fin FET = Multiple gate

- Better control of short channel effects

- Lower DIBL , drain induced barrier lowering and lower SS, subthreshold swing

- Higher ION/IOFF for fixed VDD, or lower VDD to achieve target ION/IOFF

Clear Advantages

Excellent short channel control leads to

– Lower leakage (lower DIBL drain induced barrier lowering and lower SS subthreshold swing)

– low threshold voltage variability due to low channel doping

– Less variability caused by random dopant fluctuations

– Lower operating voltage -> 50% dynamic power savings

Additional Considerations

- Quantized widths (and channel lengths)

- Body biasing totally ineffective

- Higher parasitics

- Potential Self-Heating issues

- Thermal aspects of ESD can be an issue

- Degradation and aging: NBTI a bit worse than planar

FinFET SRAMs The Good News

- Higher performance and lower leakage compared to planar

- Operates at lower Vdd than planar

- Good static noise margin at low Vdd

- Decent noise to signal ratio can be achieved (with a β=2 for example)

- Good (Low) Variability

- Read Margin and Write Margin distribution narrower than in planar

Resource : FinFETs & SRAM Design, Raymond Leung VP Engineering, Embedded Memories, April 19, 2013